Alphawave Semi宣布,已成功在台积电N2制程上完成业界首批UCIe IP子系统之一的Tape-out,实现36G晶粒对晶粒(die-to-die)间的数据传输速度。此解决方案已全面集成台积电的CoWoS技术,为次世代Chiplet架构提供突破性的带宽密度与可扩展性。

Alphawave Semi指出,随着此次Tape-out,Alphawave Semi成为业界首批能在2nm纳米片技术实现UCIe连接的企业,为开放式晶粒生态系统迈出关键一步。Alphawave Semi定制化芯片与IP部门资深副总裁暨总经理Mohit Gupta表示,很荣幸凭借N2时代领先业界,推出第一款采用这项先进制程的UCIe IP,“我们的36G子系统验证全新一代高密度、低功耗的晶粒互联技术,为未来64G UCIe与更高速率铺路,这对AI和高端交换网络应用至关重要”。

Alphawave Semi的UCIe IP子系统是基于台积电2纳米制程,可提供36G性能、11.8 Tbps/mm带宽密度,具备极低功耗与延迟,并支持先进功能,如每信道即时健康监测与完整可测试性。该解决方案符合UCIe 2.0标准,通过Alphawave Semi高度可配置且高效的流媒体协议D2D控制器(Streaming Protocol D2D Controller),并支持多种协议,包括PCIe®、CXL™、AXI、CHI等。

Alphawave Semi也积极推动关键生态系合作,以推进突破性技术,利用D2D为基础的开放晶粒互通能力,打造更广泛的AI连接平台。

台积电先进技术业务开发部资深处长袁立本表示,这一里程碑也显示,通过我们的开放创新平台(OIP)与合作伙伴Alphawave Semi密切合作,能快速提供先进的界面IP与定制化芯片解决方案,以满足日益增长的AI与云计算基础建设需求。

同时,Alphawave Semi已着手推进下一代UCIe解决方案的开发,并计划支持64G UCIe,协助AI与HPC客户在快速演进的晶粒导向生态中抢占领先地位。

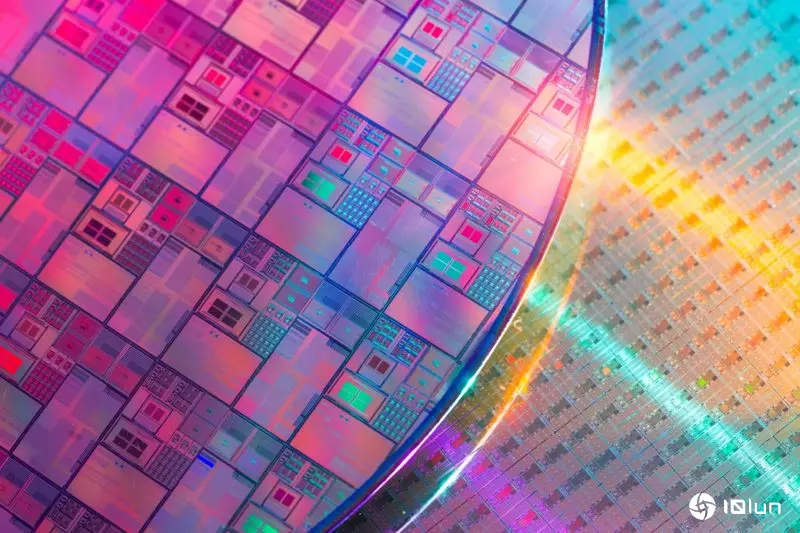

(首图来源:shutterstock)