全球半导体大厂英特尔 (Intel) 日前大型举办展示,披露其在先进封装领域的最新研发成果,推出一系列以Intel18A与Intel14A等先进节点制程的多小芯片(Multi-chiplet)产品概念。此次展示不仅展现了英特尔在Foveros 3D与EMIB-T先进封装技术上的突破,更传提交其希望在高性能计算(HPC)、人工智能(AI)及数据中心市场,与台积电的CoWoS封装技术一决高下的强烈企图心。

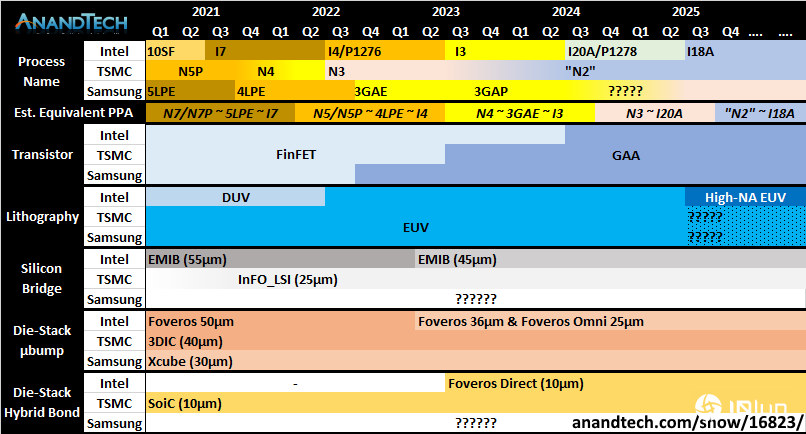

英特尔本次技术展示的核心在于其精密,且具高度扩展性的先进封装架构。根据数据显示,英特尔将利用Intel 14A-E节点制程提供突破性的逻辑性能,该制程同时采用了RibbonFET 2与PowerDirect技术。而在基础芯片部分,则采用Intel18A-PT制程,这是首款采用背后供电技术的基础芯片,能显著提升逻辑密度与电力供应的可靠性。

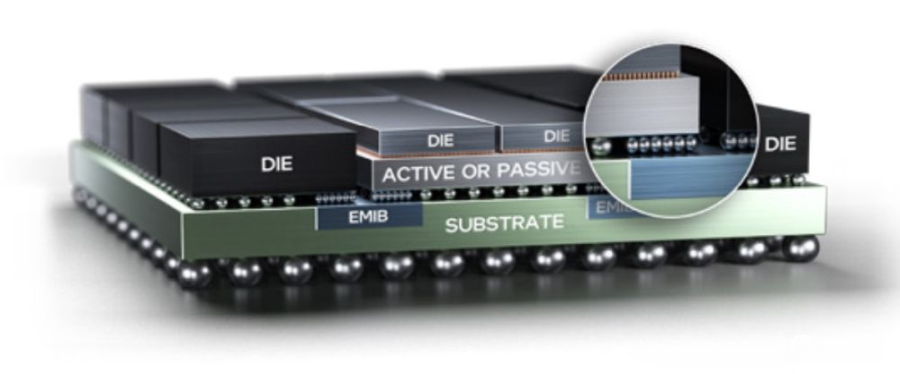

此外,为了达到极致的垂直堆栈目标,英特尔还导入了Foveros Direct 3D技术,通过极细间距的混合键合(Hybrid Bonding)进行精密3D堆栈。而在多芯片互联方面,新一代的嵌入式多芯片互联桥接(EMIB-T)技术加入了硅穿孔(TSV)技术,可提供更高的带宽,并集成更大规模的芯片组。

另外,英特尔还在展示视频中披露了两款极具前瞻性的概念设计,展现了其超越传统光罩限制(Reticle Limit)的技术实力。其中在中端解决方案方面,可配备4个运算芯片与12个HBM位点。至于在旗舰解决方案方面,则是规模扩大到16个运算芯片与24个HBM位点,并可配置多达48个LPDDR5X控制器,极大化AI与数据中心工作执行所需的内存密度。

而且,这些设计采用了类似“Clearwater Forest”的架构,其基础芯片负责搭载SRAM,并通过Foveros 3D技术将顶层包含AI引擎或CPU IP的运算芯片堆栈在上面。内存支持方面,英特尔强调其封装方案能无缝兼容目前的HBM3/HBM3E,以及未来的HBM4、HBM5等次世代标准。

根据市场的分析,英特尔这次一系列展示动作,无疑是向台积电发出挑战。台积电目前已规划9.5倍光罩尺寸的CoWoS解决方案,并结合A16制程,以及超过12个HBM4E位点(CoWoS-L)。然而,英特尔表示,其封装架构具备超过12倍的光罩尺寸,显示在规格上有意超越对手。英特尔还特别强调,虽然Intel18A制程主要用于其内部产品,但intel 14A节点制程则是专为外部客户设计的。因此,英特尔目前正积极与产业伙伴创建多样生态系,目的是提供更快的上市时间与更具韧性的供应链。

尽管英特尔过去在先进封装领域早有建树,例如被视为工程奇迹的Ponte Vecchio芯片,但受限于良率问题与研发延迟,该产品并未取得商业化上的成功,随后如Falcon Shores等多项计划也遭取消。因此,目前英特尔正试图凭借Jaguar Shores,以及备受期待的Crescent Island AI GPU卷土重来。对英特尔而言,真正的考验在于能否成功争取到第三方客户的订单。尤其在Intel14A技术与先进封装解决方案的加持下,英特尔似乎已准备好重新回归芯片代工市场的顶尖赛局。

(首图来源:英特尔提供)