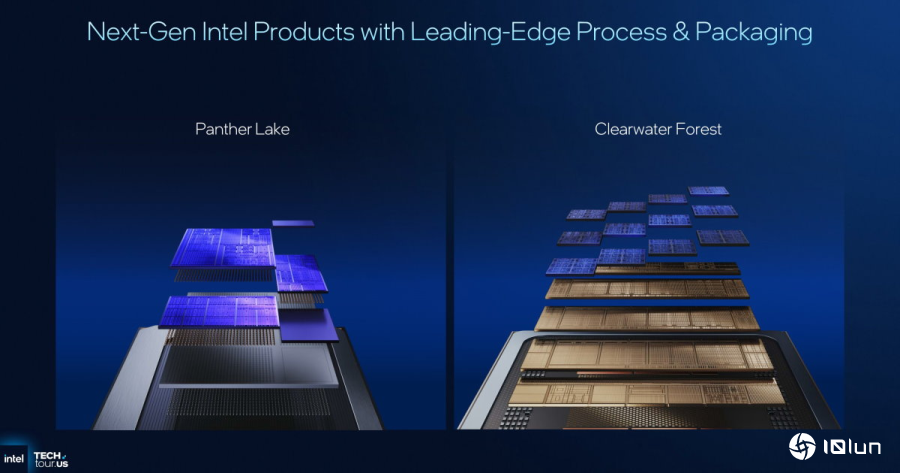

Intel在Panther Lake与Clearwater Forest等处理器使用Intel 18A制程节点,导入RibbonFET与PowerVia等技术,同时借由先进封装将多种模块组合成单一处理器。

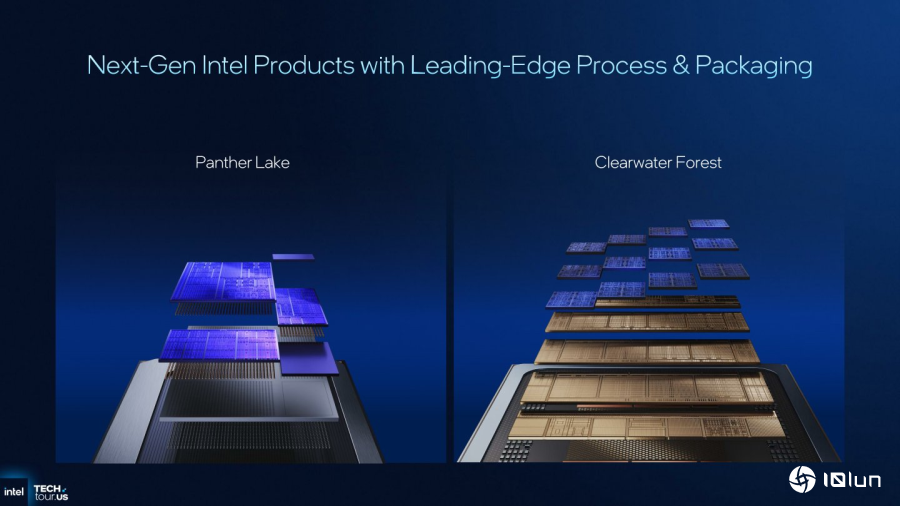

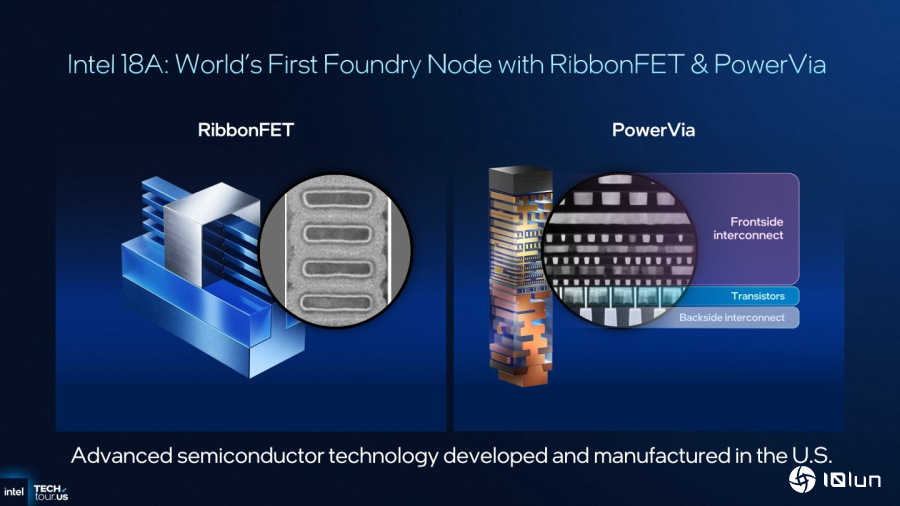

Intel 18A制程节点的2大亮点在于业界首次应用于量产产品的RibbonFET(环绕式闸极,也称为Gate All Around,GAA)与PowerVia(晶背供电)等技术,达到微缩晶体管尺寸,并改善芯片内部电力与信号的传输品质,进一步缩小芯片尺寸(或在相同尺寸放入更多晶体管),以及节省运行时消耗的电力。

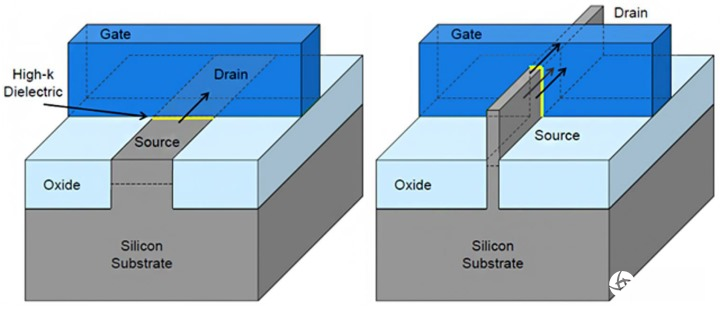

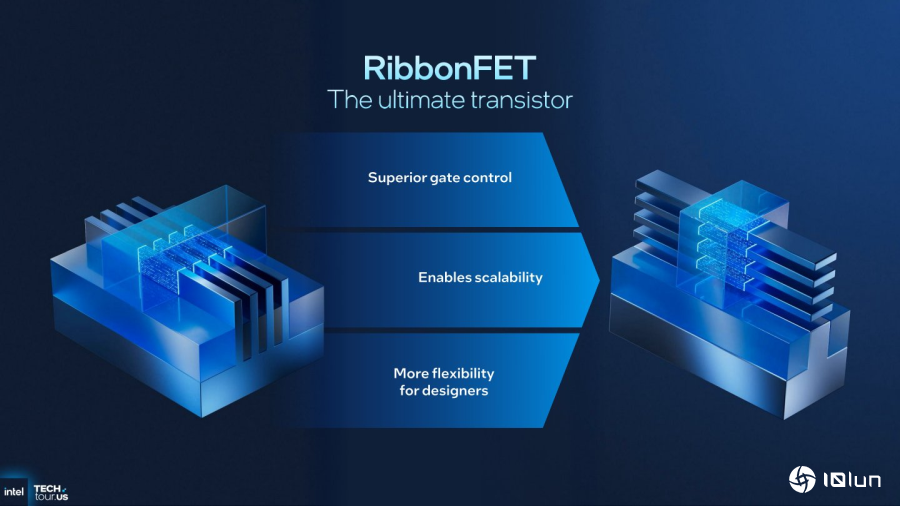

回顾FET(Field-Effect Transistor,场效晶体管)的发展过程,在早期的平面式设计中,通过改变闸极(Gate)的电压来控制源极(Source)与汲极(Drain)的电流导通与否,而闸极长度就是我们所说的“几纳米制程”。

随着晶体管的尺寸越缩越小,闸极的尺寸小到无法精准控制电流,后续发展出的FinFET(鳍式场效晶体管)则将晶体管外形改为就像鳍片的立体结构,在相同尺寸的前提下能够通过3个面来增加闸极与源极的接触面积,强化控制电流的能力,有助于持续微缩晶体管尺寸。

Panther Lake与Clearwater Forest等处理器使用目前最先进的Intel 18A制程节点。

Panther Lake与Clearwater Forest等处理器使用目前最先进的Intel 18A制程节点。

Intel 18A制程节点导入RibbonFET环绕式闸极与PowerVia晶背供电等2大技术。

Intel 18A制程节点导入RibbonFET环绕式闸极与PowerVia晶背供电等2大技术。

Lam Research(科林研发)提供的视频中,可以看到平面式FET、Fin FET、RibbonFET(即GAA)的差异。

传统FET在闸极与源极之间只有1个接触面,其中黄线部分即为闸极长度。FinFET晶体管的立体结构则有3个接触面,而能延长闸极长度。

传统FET在闸极与源极之间只有1个接触面,其中黄线部分即为闸极长度。FinFET晶体管的立体结构则有3个接触面,而能延长闸极长度。

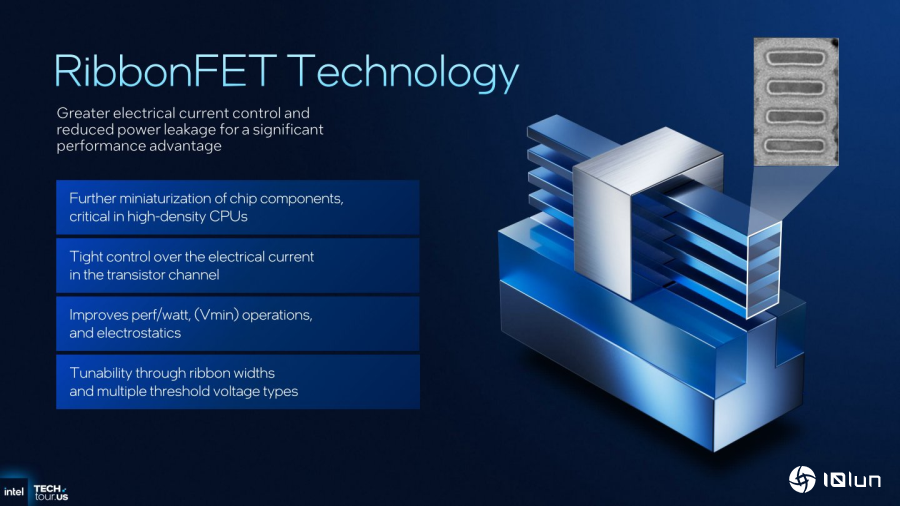

RibbonFET进一步提升至4个接触面,能增加接触面积而改善电流控制能力。

RibbonFET进一步提升至4个接触面,能增加接触面积而改善电流控制能力。

从右上角的显微照片可以看到RibbonFET源极的4个面与闸极都有接触。更强的电流控制能力也代表可以提高性能同时节省电力

从右上角的显微照片可以看到RibbonFET源极的4个面与闸极都有接触。更强的电流控制能力也代表可以提高性能同时节省电力

RibbonFET进一步让闸极提升到4个接触面,更加强化电流控制能力,对于密度不断提高的芯片而言相当重要。RibbonFET同时也能改善漏电情况,提升电力效率、最低工作电压(Vmin)、静电特性等等,带来更显著的性能优势。未来RibbonFET还能通过调整不同的鳍片宽度和多种阈值电压(Vt)类型,针对需要极致省电,或是可以通过提高功率催出更高性能的不同使用场景,提供更广泛的设计弹性。

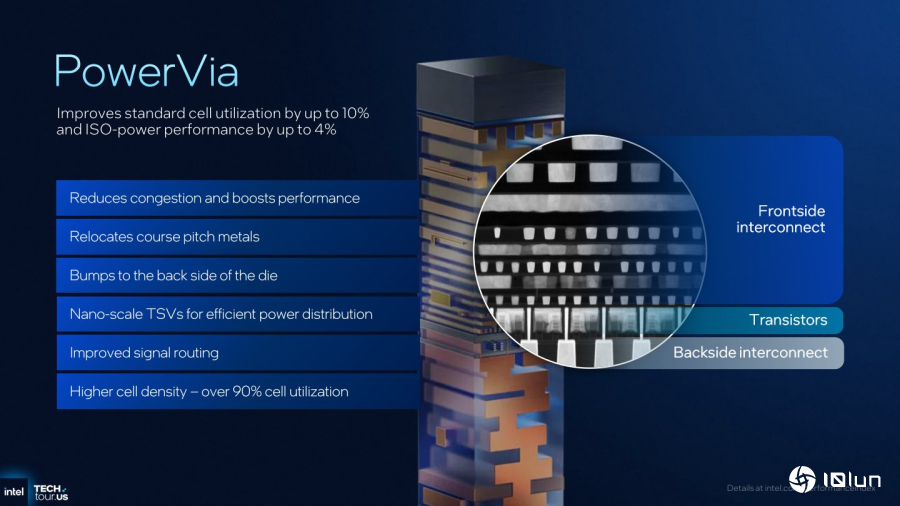

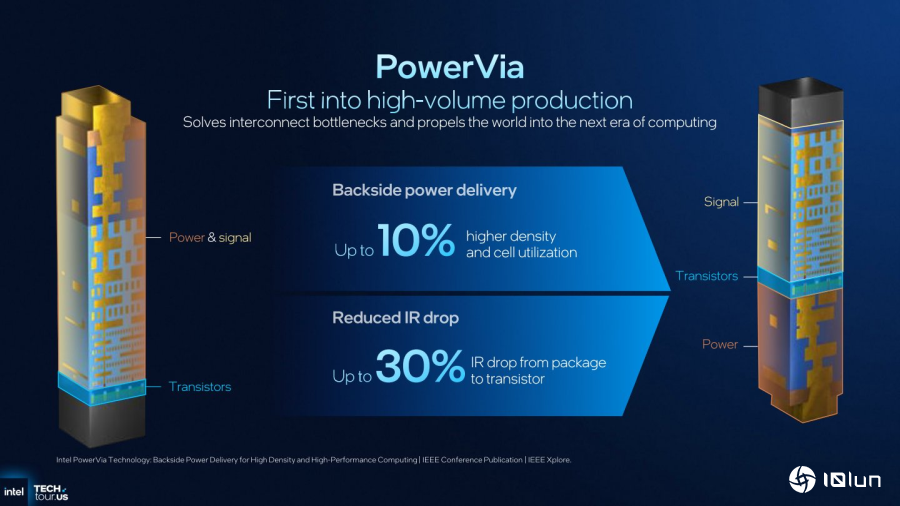

随着晶体管密度不断提高,原本放置于在芯片正面的信号和电源布线会相互干扰并影响性能,而PowerVia技术则是将电源布线改置于在芯片背面,将较粗的金属线路和凸块移至芯片背面,并在每个标准单元内置纳米级硅穿孔(nano-TSV),以达到更有效率的电源分配,并降低固有电阻导致的电压下降。PowerVia能提升5-10%的标准单元利用率,并在相同功耗下带来最高4%的性能增益。

Intel表示Intel 18A制程节点是北美最早实现量产小于2纳米的先进制程节点,相校于Intel 3制程节点,电力效率提高15%,芯片密度提高30%,并全面支持业界标准的EDA工具(Electronic Design Automation,电子设计自动化),与超过35家领先业界的生态系统合作伙伴共同致力于确保广泛的客户能够顺利采用Intel的解决方案。

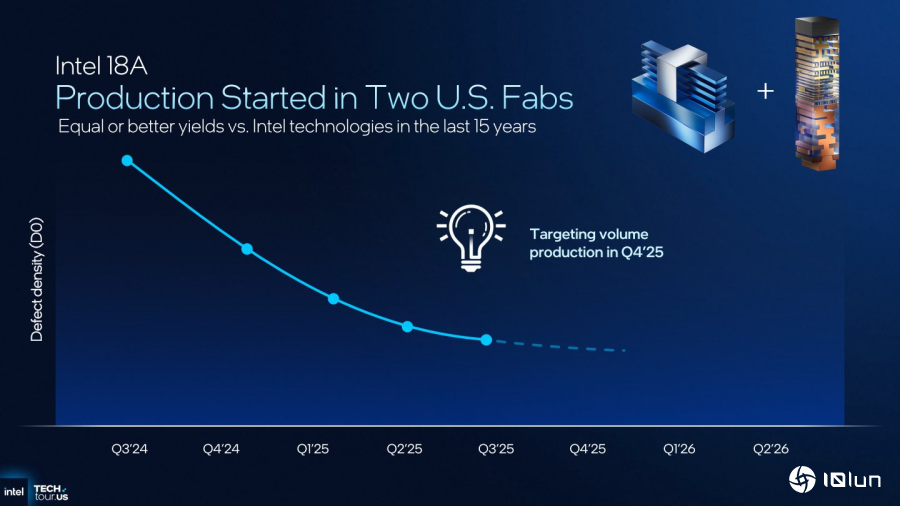

值得注意的是,Intel在2025年7月24日的第2季财报中提到,在Intel 18A制程节点的良率与性能方面持续有所进展,虽然没有给出明确数字,但表示良率优于过去15年间各类制程的表现,将成为未来至少3代Intel客户端与服务器产品的基础,具有相对乐观的财务状况,仅靠有自家品就能带来合理的投资回应。而下一代Intel 14A制程节点则是专为代工业务所设计的制造节点,用以满足客户的特定需求,并触及更广泛的市场。

PowerVia技术则是将电源布线置于在芯片背面,改善信号和电源会相互干扰的影响。

PowerVia技术则是将电源布线置于在芯片背面,改善信号和电源会相互干扰的影响。

PowerVia最高能提升10%的标准单元利用率,并改善30%电源电压降(IR Drop)。

PowerVia最高能提升10%的标准单元利用率,并改善30%电源电压降(IR Drop)。

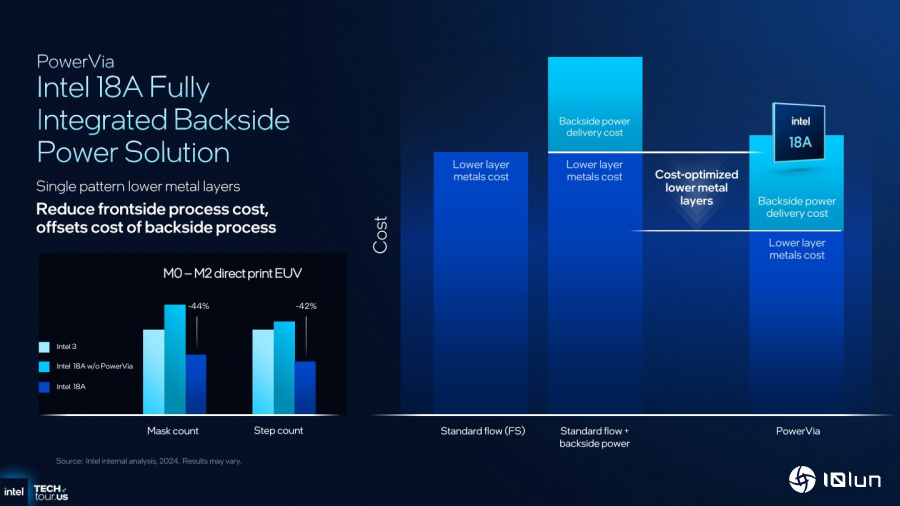

Intel通过改善底层金属原料的成本,来弥补导入PowerVia所产生的额外成本,以提升制程的价格竞争力。

Intel通过改善底层金属原料的成本,来弥补导入PowerVia所产生的额外成本,以提升制程的价格竞争力。

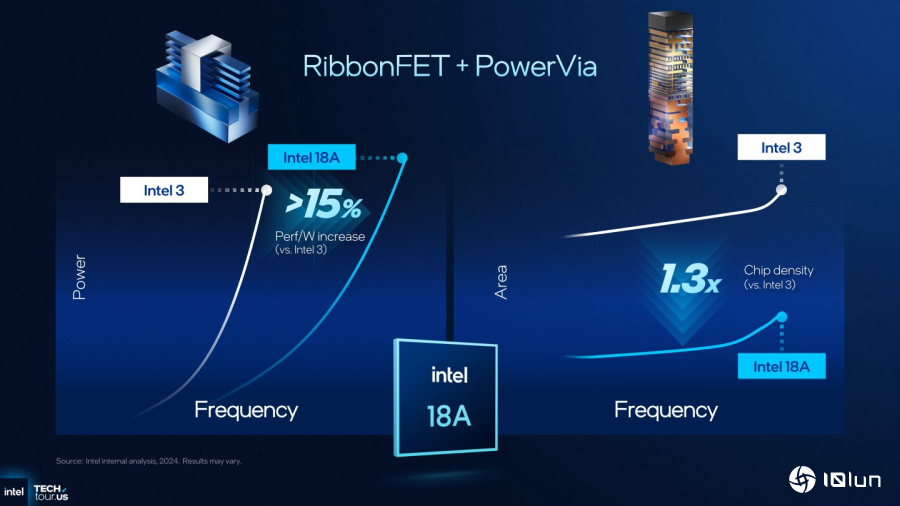

与Intel 3制程节点相比,Intel 18A制程节点电力效率提高15%,芯片密度提高30%。

与Intel 3制程节点相比,Intel 18A制程节点电力效率提高15%,芯片密度提高30%。

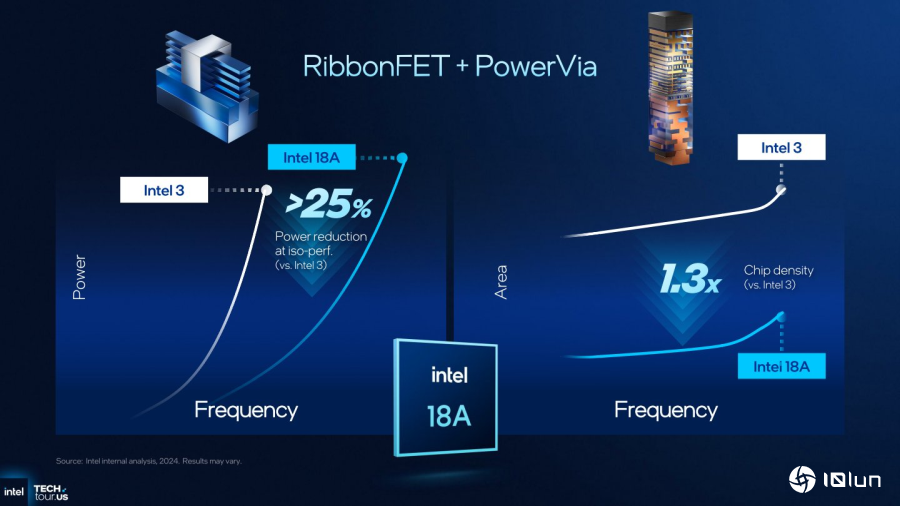

另一方面,在相同性能的前提下,Intel 18A制程节点能较Intel 3制程节点节省25%电力。

另一方面,在相同性能的前提下,Intel 18A制程节点能较Intel 3制程节点节省25%电力。

Intel表示18A制程节点的良率优于过去15年间各类制程的表现,并将于2025年第4季开始量产。

Intel表示18A制程节点的良率优于过去15年间各类制程的表现,并将于2025年第4季开始量产。