随着人工智能(AI)芯片和高性能计算(HPC)需求的爆发,半导体产业正加速迈向异质集成与先进封装的时代。传统上,微影技术多聚焦于前端芯片制造,然而,后段封装所需的微影制程能力,已成为下一代系统单芯片(SoC)设计的关键瓶颈。为了解决芯片尺寸不断扩大及芯片翘曲(warpage)带来的制程难题,全球微影设备领头羊艾司摩尔(ASML)近日宣布推出新型微影机台XT:260,大幅扩大了曝光场(Exposure Field)的范围,显著提升先进封装制程的效率与良率。

ASML表示,现代芯片设计越来越依赖垂直与水平的“堆栈方式”来实现更强大的功能与更高的带宽。这类堆栈通常包含多种异质组件,例如在处理器单元中,最新的GPU(例如B200)或CPU。这些组件可以进行混合搭配(mix and match)。而在内存领域,DRAM被垂直堆栈后形成所谓的HPM(High-Performance Memory),这是高带宽内存(HBM)的简化说法。

最后在光电集成的共封装光学(CPO)上,虽然尚未量产,但ASML认为这是未来几年内将发生的重要技术转折点。在这些复杂的结构中,中介层(interposer)扮演了关键的桥接作用。尤其是中介层上布有电路,因此必须进行曝光制程才能将电路图案打出来。

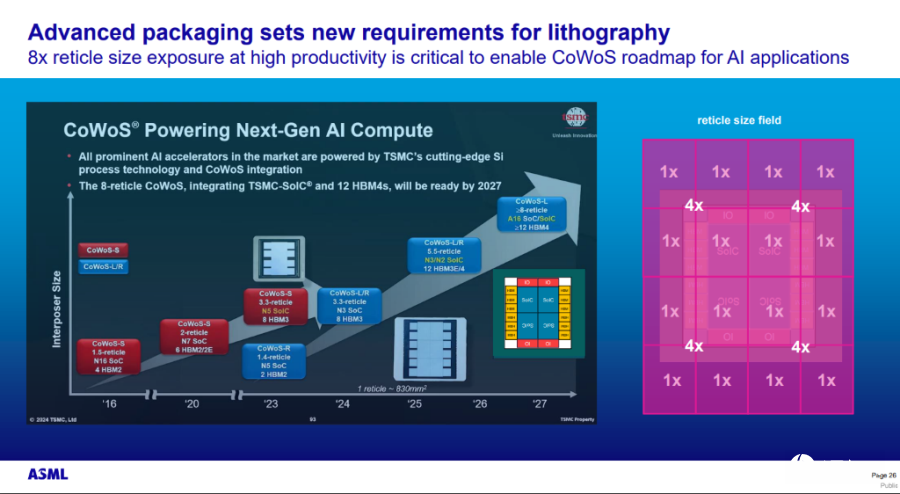

ASML指出,根据台积电(TSMC)的技术蓝图(Radow Map),业界普遍使用“光罩尺寸(reticle size)”来衡量中介层的大小。一个reticle size可以被视为一个单位的面积。目前业界的组装尺寸大约在3.x片到5.x片光罩大小的水准。然而,技术发展目标预计将做到大约八片光罩大小。对此,ASML强调,随着尺寸的增加,传统微影机台面临两大核心挑战。

首先是曝光场限制,由于传统微影机台的单次曝光场范围有限,若要处理多达八倍光罩大小的大型中介层,必须分区多次进行曝光。这会大幅降低制造效率。第二个挑战就是芯片翘曲(Warpage),因为在先进封装的世界里,有一条与微观世界相反的规律,那就是“尺寸越大,制程难度越高。”当许多不同芯片被放置在一起时,由于不同材料的热膨胀系数不一致,芯片在受热后会发生弯曲,即产生翘曲。微影设备必须具备处理这种弯曲芯片的能力。

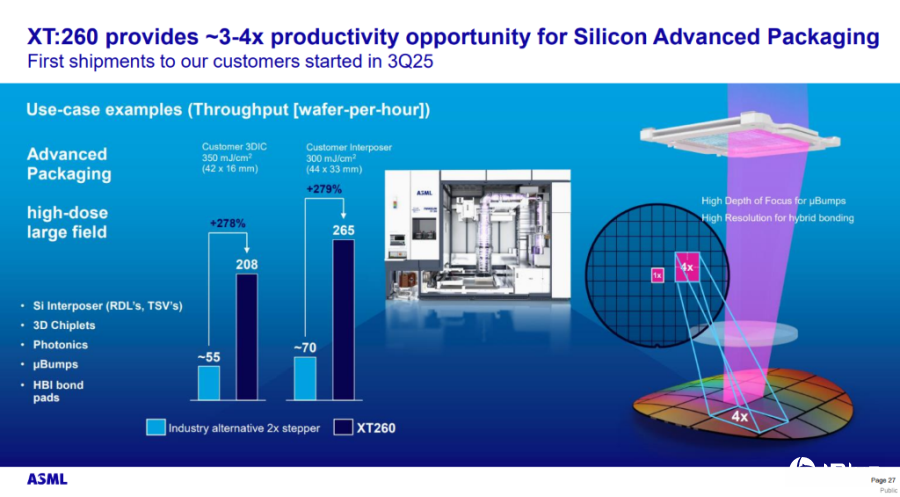

为应对上述挑战,ASML于2025年推出了XT:260新机台。这台新设备的核心突破在于显著扩大了曝光场的大小,从而使曝光效率获得大幅提升。根据ASML展示的数据显示,XT:260机台的D.P.(产出率)表现相较于竞争对手的设备呈现出大幅度的提升。此外,XT:260特别具备处理翘曲芯片的能力。这项技术突破使得机台能够适应因异质集成导致的芯片弯曲问题。

ASML表示,这项成果是公司的一个“非常重要的里程碑”,因为它代表ASML在过去较少被提及的后段封装领域投入了大量的时间进行研发。另外,XT:260的应用层面极广,不只包含中介层(interposer),还包括3DIC(三维集成电路),台积电称之为SoIC(System-on-Integrated-Chips)的相关技术。还有光电集成的CPO部分的应用案例。这些方向与ASML所提及的“全方位微影(holisticography)”的概念相同,暗示未来的微影技术将是一个系统性的集成解决方案。

(首图来源:ASML提供)