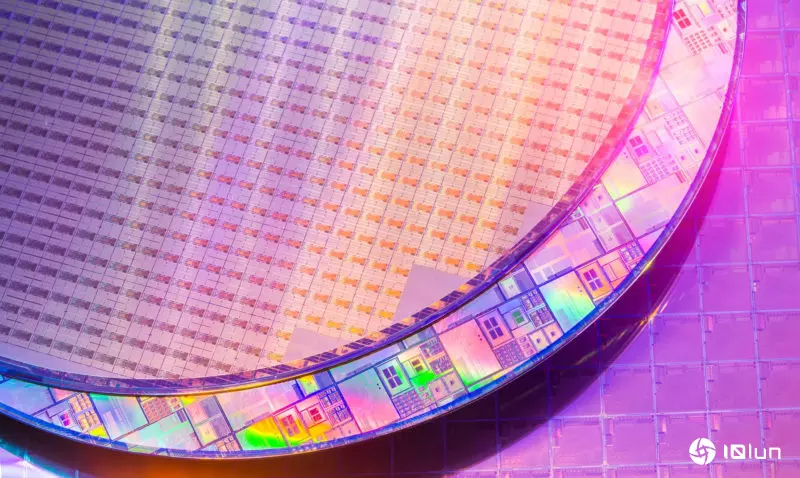

扇出型面板级封装(FOPLP)被誉为下时代先进封装显学,芯片代工龙头台积电、半导体封测一哥日月光、内存封测龙头力成等半导体三强都积极卡位,抢食英伟达、超微等大厂庞大的高速运算芯片高集成先进封装商机。

半导体三强扇出型面板级封装领域大进击,各有盘算,引爆新一波抢单大战。

台积电技术名为CoPoS(Chip-on-Panel-on-Substrate),产能落脚嘉义,2026年设实验线。日月光高雄已有一条量产300×300mm面板级封装产线;力成耕耘最久,早在2019年实现量产,定名PiFO(Pillar integration FO)。

业界分析,高速运算芯片高度集成各有优势,面板级扇出型封装相较芯片,基板面积较大且可异质集成,集成载有5G通信滤波功能的电路设计,封装后芯片性能与功能大幅提升,更适合5G通信、物联网设备等各种产品,有助各种消费性电子产品体积再缩小。

台积电CoPoS主要聚焦AI与高速运算(HPC)应用,外传2028年量产。是CoWoS“面板化”转成方形设计,有利芯片产能扩大。台积电北美技术论坛端出最新A14制程,也预告2027年量产9.5倍光罩尺寸CoWoS,能把更多逻辑与内存芯片集成至一个封装,业界预估趋势吻合CoPoS发展。

日月光已有一条量产的300×300mm面板级封装产线,采FanOut制程。

力成将旗下扇出型面板级封装技术定名PiFO,技术类似台积电CoPoS。

(首图来源:shutterstock)