近年来,2纳米制程成为半导体产业兵家必争之地,台积电、三星与Intel等巨头纷纷加快脚步。除了这些领头羊之外,日本创业公司Rapidus也在近几个月声势大涨,成为全球市场高度关注焦点。

根据爆料人士透露,Rapidus的2HP制程节点逻辑密度达237.31 MTr/mm²,几乎与台积电N2的236.17 MTr/mm² 相同。Rapidus采用了高密度(HD)单元库,单元高度为138单位,并采用G45 pitch。由于N2与2HP都属于HD风格的单元设计,显示双方皆以追求最大逻辑密度为目标,也就是说,在相同面积下能放入更多晶体管,最终可实现的运算功能也相当接近。

Raipidus share the data with 2nm(Named 2HP)

so that,we can know the NEXT Gen process technology in Logic Density

— Kurnal (@Kurnalsalts) August 31, 2025

两家公司同样采用GAA(Gate-All-Around)环绕式闸极,不过在细节上有所不同。台积电的N2尚未计划导入背面供电网络(BSPDN),预计要到后续的N2P版本才会考虑;Rapidus则已明确表态,将在2HP上直接引入BSPDN技术。

至于制程方式上, Rapidus选择单芯片(single-wafer)处理,芯片一次一片处理,强调在小规模生产中快速调整的灵活性;台积电则延续多芯片(batch)生产,以支撑大规模量产。

另外,在产业生态上,双方的差距更为明显。Rapidus虽已与IBM、Cadence等展开合作,但整体仍处于起步阶段,产业支持度明显不足。相比之下,台积电早已形成完整的EDA、IP与客户链,合作伙伴涵盖Apple、NVIDIA与AMD等国际大厂,拥有更完整且成熟的生态系统。

Rapidus计划在2026年第一季发布基础设计组件(PDK),并将目标锁定于2027年量产。而台积电预计2025年第四季量产2纳米。业界人士指出,Rapidus仍握有大约两年期限来证明实力,若无法在进程内展现成果,恐将失去竞争机会并被迫退出市场。

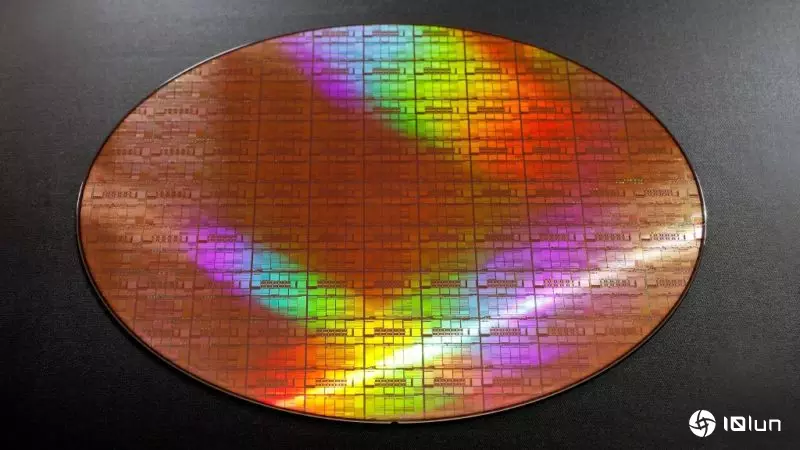

(首图来源:Rapidus)