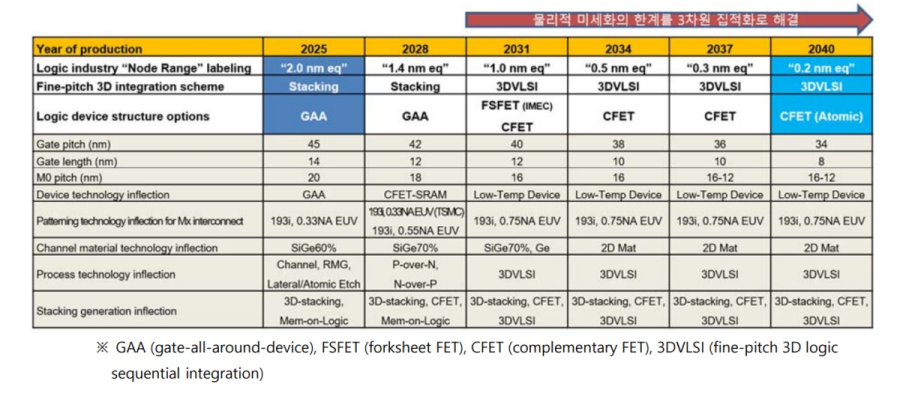

根据韩国半导体工程师协会发布的《반도체 기술 로드맵 2026》(半导体技术路线图2026),全球半导体产业正规划在未来15年内,将先进逻辑制程从现行的2纳米节点,逐步推进至2040年的0.2纳米,正式进入埃米(Å)时代。随着传统线宽微缩逐渐逼近物理极限,未来制程演进将不再仅依赖微影技术,而是转向结构、材料与系统层级的全面革新。

2040后将迎来埃米时代,EUV可能迎来瓶颈从时间轴来看,路线图预期2025年左右进入2纳米时代,并于2031年前后推进至1纳米级;到了2040年,逻辑电路线宽将进一步缩小至0.2纳米。尽管0.75NA EUV可在2030年前后带来更细线宽,但基于微影的物理微缩将逐步趋于饱和,制程竞争的重心势必转向芯片架构与整体系统设计。

(Source:ISE,同下)

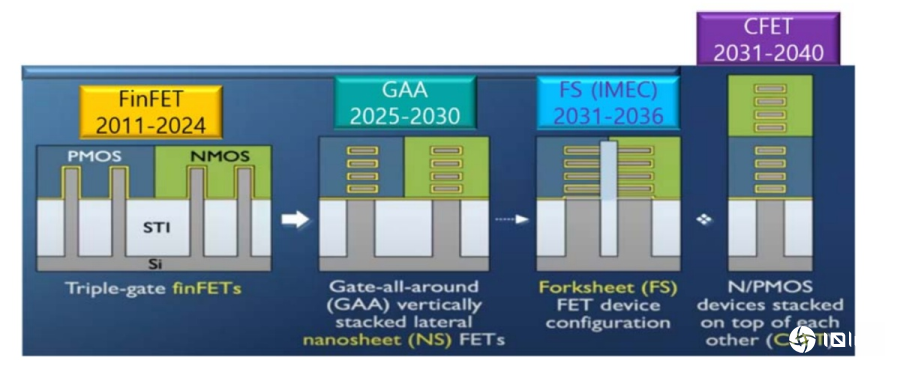

晶体管与制程朝向立体化为延续摩尔定律,逻辑组件将由FinFET转向GAA(Gate-All-Around),并进一步演进至CFET(Complementary FET) 等三维晶体管结构,通过将PMOS与NMOS垂直堆栈,突破平面密度限制。配合Monolithic 3D(单晶3D) 制程,以及由DTCO迈向STCO(系统-制程共同优化) 的设计思维,未来性能提升将来自整体架构重整,而非单一制程节点的微缩。

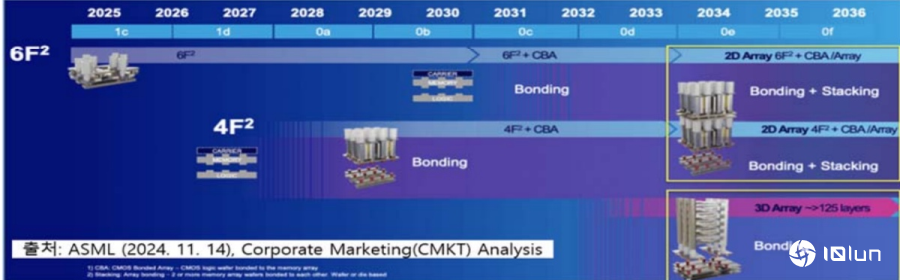

除了逻辑制程,内存技术的演进节奏与0.2纳米逻辑制程高度同步。在DRAM领域,传统BCAT架构预期将在7~8纳米遭遇微缩极限,未来将转向垂直信道晶体管、堆栈式DRAM、4F² 单元,以及通过Hybrid Bonding将CMOS电路直接与内存数组结合的CBA(CMOS Bonded Array) 架构,延续密度与性能提升。

在AI应用推动下,高带宽内存(HBM) 的重要性进一步放大。路线图指出,HBM将通过更高层数堆栈、混合键合与散热设计,HBM预测2031年将有20层、8 TB/s,并在2040年达到30层以上、128 TB/s的带宽水准。。

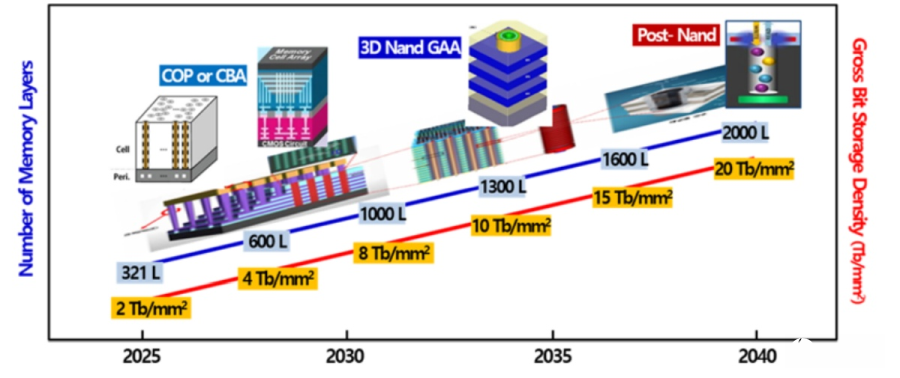

至于NAND Flash,则走向“以层数换密度”的发展路径,预期自321层,推进至2031年约1,000层,并在2040年挑战2,000层。

半导体产业正借由逻辑与内存的3D化、Hybrid Bonding及系统级架构重整,提升单位面积集成密度并降低互联延迟,以在不依赖线宽微缩的情况下,满足未来AI或其他产业对于高速、低功耗的需求。

(首图来源:AI生成)