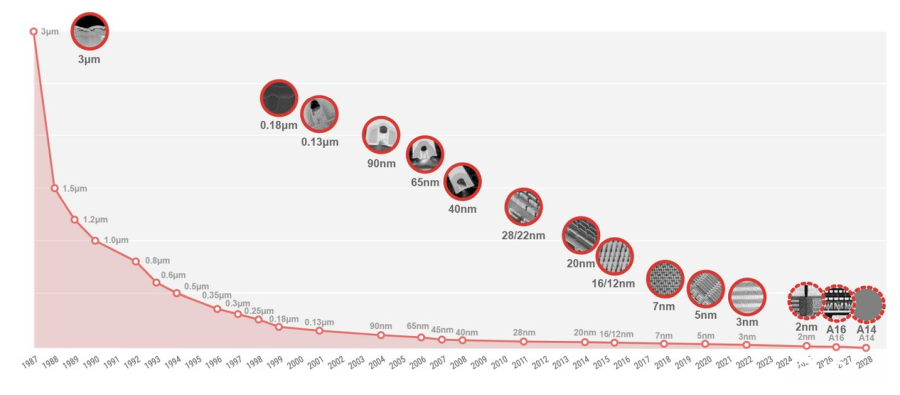

芯片代工龙头台积电以一种极为低调的方式,正式声明了2纳米(N2)时代的来临。与以往重大制程突破时举行盛大庆祝活动或发布正式新闻稿的做法不同,台积电此次选择在其官方网站的技术页面上,静悄悄地更新了一行文本,那就是“台积电2纳米(N2)技术已按计划于2025年第四季开始量产”。这份低调并未掩盖其战略意义,随着N2制程的投产,全球半导体竞争已进入了以GAA(全环绕闸极)架构为核心的新纪元。

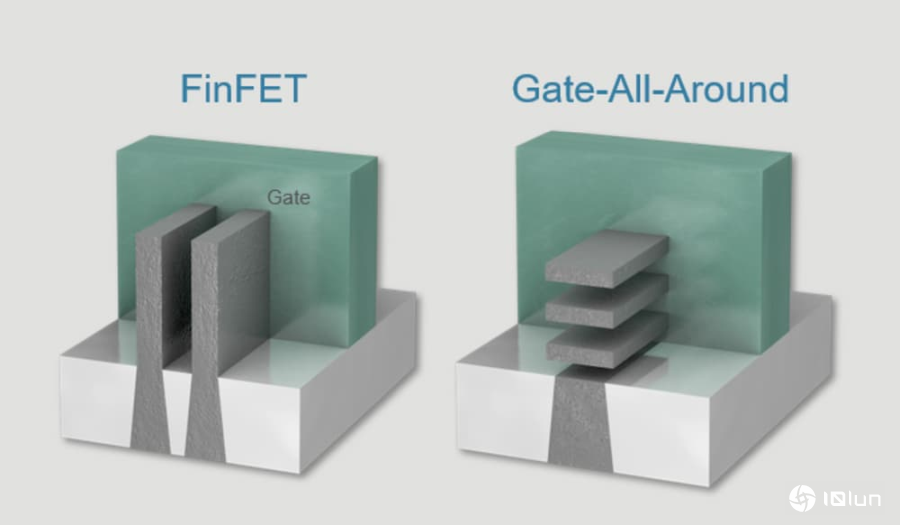

从FinFET到GAA的技术突破台积电的N2制程不仅仅是数字上的进步,更是技术底层逻辑的重大革新。这是该公司首个采用全环绕闸极(Gate-all-around,GAA)纳米片(Nanosheet)晶体管的制程节点。在这种新结构中,闸极完全包覆由堆栈水平纳米片形成的信道,这种几何构造能显著提升电磁控制力,有效减少漏电问题,并允许在不牺牲性能或功耗效率的前提下,进一步缩小晶体管尺寸,进而大幅增加晶体管密度。

根据台积电公布的技术参数,与前一代N3E制程相较,N2在相同功耗下可提升10%至15%的性能。若在相同性能下,则能降低25%至30%的功耗。对于混合设计(包含逻辑、模拟与SRAM)而言,其晶体管密度可提升15%。而针对纯逻辑设计,密度增幅更高达20%。

此外,N2制程还导入了超高性能金属绝缘体金属(SHPMIM)电容器,这项创新为供电网络提供了比前代设计高出两倍以上的电容密度,同时将片电阻(Rs)与通孔电阻(Rc)各降低了50%。这些技术细节的改进,直接转化为更稳定的供电、更卓越的运算性能以及更优化的整体能源效率。

高雄厂的惊喜与新竹厂的续进此次2纳米量产最令业界意外的,莫过于生产基地的选择。原本外界普遍预期,台积电会率先在紧邻其全球研发中心的新竹宝山Fab 20厂进行N2技术的量产,毕竟该厂区是2纳米系列技术的研发大本营。然而,根据最新的运营资讯,台积电实际上是从位于高雄的Fab 22厂开始量产2纳米芯片。

虽然Fab 20厂预计也会随后启动大规模生产,但高雄厂的“首发”地位,反映出台积电在全台产能调配上的高度灵活性。台积电首席执行官魏哲家在10月的法人说明会上曾经表示,N2制程在本季进展顺利且良率良好,并预计在2026年受益于智能手机与高性能运算(HPC)AI应用的驱动,完成更快速的产能提升。

过去,台积电在导入新制程时,通常会优先针对移动设备及小型消费性电子产品进行产能爬坡,因为这类芯片尺寸较小,良率控制相对容易,但N2制程打破了这项惯例。背景是因为市场对先进制程的强烈需求,台积电正同时针对智能手机,以及更大型的“AI”与“HPC”设计在新厂进行产能提升。

尽管HPC是一个广义词汇,涵盖了从游戏主机系统单芯片(SoC)到重型服务器中央处理器(CPU)的所有产品,但这无疑增加了产能提升的复杂性。而且,同时启动两座具备N2生产能力的芯片厂,反映出台积电众多合作伙伴对此技术的高度兴趣。

N2P与A16的后续接力2纳米的量产只是开端,台积电已规划好了清晰的后续路径。先前魏哲家透露,作为N2家族的延伸,台积电将推出N2P制程,在N2的基础上进一步优化性能与功耗,预计于2026年下半年量产。

更受瞩目的将是A16制程,通过A16结合N2P的技术,并导入台积电引以为傲的超级电轨(Super Power Rail,SPR)背面供电技术。这项技术特别适用于具有复杂信号路径和密集电力传输网络的高性能运算产品。目前,A16的研发进度也符合预期,预计将于2026年下半年进入量产阶段。

台积电2纳米的正式量产,代表着半导体产业在追求摩尔定律极限的道路上又迈出了关键一步。从高雄厂的异军突起到GAA架构的实战应用,台积电再次证明了其在先进制程领域的执行力。如果把半导体制程的演进比喻成一场马拉松,那么N2制程的量产就像是运动员穿上了特定的轻量化跑鞋(GAA架构),在减轻负担(功耗降低)的同时,还能爆发出更强的冲刺力(性能提升)。随着AI与HPC芯片的需求爆发,这场竞赛的下半场才正要进入最高潮。

(首图来源:shutterstock)