随着半导体制程迈向3纳米以下节点,先进制程微缩技术已逐步逼近物理极限。日前英特尔(Intel)高层却罕见公开指出,芯片制造流程未来将不再围绕“光罩技术”打转,而是由晶体管架构根本性变革所主导,这发这也让ASML新一代的High-NA EUV的广泛采用添加了隐忧。

根据投资研究平台Tegus分享于X的一段高层访谈内容,该名英特尔主管强调,随着GAAFET(环绕闸极)与CFET(互补式FET)等新一代晶体管架构渐趋成熟,芯片制程的关键控制点,将从分辨率极限的光罩工序,转向精密的蚀刻(Etching)与材料沉积(Deposition)技术,进一步降低对新一代的High-NA EUV(advanced lithographic equipment)的依赖。

Director at Intel explains why ASML has been struggling due to GAA, and will struggle with the move to CFETs as well (via Tegus). The bright spot in terms of order flow can be high-NA adoption later this decade, or EUV multiple patterning, but clearly order flow will be highly…

— Tech Fund (@techfund1) June 16, 2025

High-NA EUV曾被视为新一代制程应用的关键设备,2024年英特尔抢先台积电和其他大厂,根据《TheElec》报道,英特尔已取得ASML的五台High-NA EUV的产能,预计将应用于其18A与14A,并今年两台已经在慢慢地投产。由于ASML每年的High-NA EUV产能约为五到六台,说明了英特尔几乎垄断了初期的产量,这说明了英特尔想要强势重回半导体领先地位的野心。

然而,“Intel Foundry Direct 2025”大会上,说明了尚未完全承诺将High-NA EUV用于量产,并保留以传统Low-NA EUV(低数值孔径) 为基础的备用制程流程,以降低风险。有报道指出,ASML已向三家客户交付总共5台高NA设备,包括英特尔、台积电以及韩国三星,不过要2025下半年才能交货。

除了英特尔以外,台积电也已经有一台High-NA EUV ,并给予价格的折扣。然而今年台积电资深副总经理暨副共同首席运营官张晓强日前在说明即将推出的A14制程时坦言,该节点“不一定”会采用ASML最新一代High-NA EUV曝光机。除指出High-NA EUV太贵抬高成本外,也不需用到此设备也能维持类似复杂度。

而据韩媒报道三星电子和SK海力士的计划,DRAM将迈向3D DRAM,3D DRAM则无需使用High-NA或Low-NA EUV设备。不同于传统DRAM,3D DRAM通过“垂直堆栈”的方式来提升晶体管密度,因此使用ArF微影技术即可,无需依赖EUV设备。

根据路透社报道,最新的High NA约3.78亿美元,相比之下,ASML现有的EUV设备售价约为2亿欧元。High NA微影工具预计能将芯片设计缩小至三分之一,提高密度与性能,但企业也需审慎评估其高昂成本是否值得。

随着芯片的尺寸所需投入的技术与资本成本却急剧上升,High-NA的导入是否仍具经济效益?当制程微缩逐渐迈入极限,未来半导体技术的突破,或许将转向更具经济效率的创新路径。

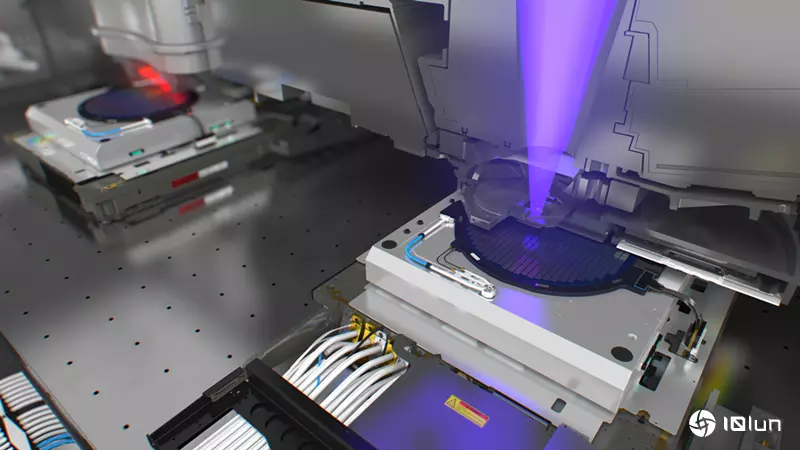

(首图来源:ASML)