18日台积电在说明会上表示,3纳米制程出货占台积电2024年第一季芯片销售金额的9%,5纳米制程出货占全季芯片销售金额的37%,7纳米制程出货则占全季芯片销售金额的19%。总体而言,先进制程 (7纳米以上先进制程) 营收达到全季芯片销售金额的65%。至于,最先进的2纳米制程,预计2025年芯片正式量产下线,2026年开始进一步贡献营收。

台积电表示,在2纳米的N2制程技术在解决对节能运算永无止境的需求方面皆领先业界,而几乎所有的AI创新者都正在与台积电合作。因此,观察到客户对N2制程技术的高度兴趣和参与,并预期整体2纳米制程技术在头两年的产品设计定案 (tape outs) 数量将高于3纳米和5纳米制程技术的同期表现。

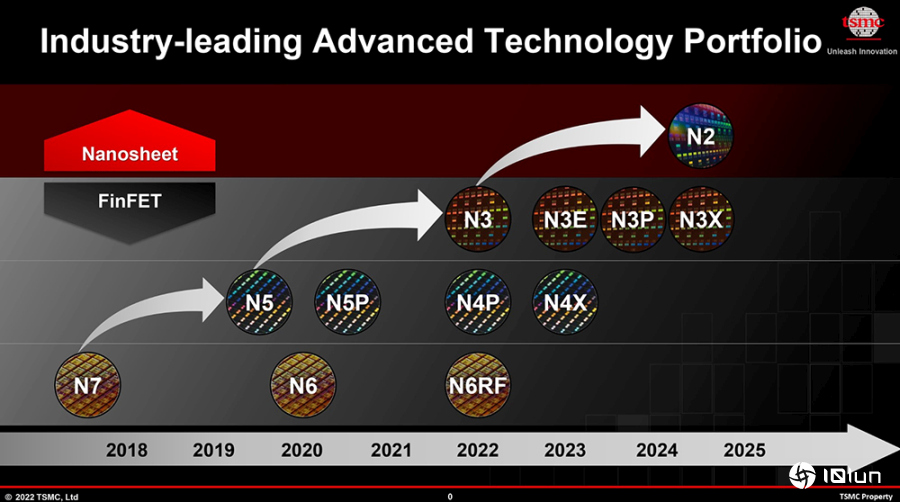

台积电强调,2纳米技术将采用纳米片 (Nanosheet) 晶体管结构,在密度和能源效率上都会是业界最先进的半导体技术。而当前N2制程技术研发进展顺利,设备性能和良率皆按照计划甚或优于预期。因此,N2制程技术将如期在2025年进入量产,其量产曲线预计与N3相似。随着持续强化的策略,N2制程技术及其衍生物科技术将进一步扩大台积电的技术领先优势,并让公司得以在未来很好地掌握AI相关的增长机会。

对于台积电持续发展2纳米制程技术,台积电重申公司在2024年的资本预算预计将介于280亿至320亿美元之间,借持续投资以支持客户的增长。而在2024年约280亿至320亿美元的资本支出中,约70-80%将用于先进制程技术,约10-20%将用于特殊制程技术。另外,约10%将用于先进封装、测试、光罩制作及其他项目。

而有鉴于强劲的HPC和AI相关需求,台积电也持续拓展全球制造足迹,以继续支持美国客户的增长、增加客户,信任并扩大台积电的未来增长潜力,具有其策略重要性。其中,在美国亚利桑那州,在获得了美国客户的坚定承诺和支持之后,计划设立三座芯片厂,这有助于创造更大的规模经济。预计,在亚利桑那州每一座芯片厂的洁净室面积都约是业界一般逻辑芯片厂的两倍大。

除了在第一座芯片厂取得了重大进展,也就是已经在4月进入采用N4制程技术的工程芯片生产 (engineering wafer production)。台积电指出,按照计划在2025年上半年开始量产。另外,继先前宣布的3纳米技术,第二座芯片厂已经升级加入采用2纳米技术,以支持强劲的AI相关需求。最近台积电也完成了第二座芯片厂上梁,即将最后一支结构钢梁放置到位,并预计于2028年开始生产。

至于,先前宣布计划在亚利桑那州建造第三座芯片厂的部分,预计采用2纳米或更先进的制程技术,预计在21世纪20年代底进行生产。台积电强调,相信一旦芯片厂开始量产,台积电将能够在亚利桑那州的每一座芯片厂提供与台湾芯片厂相同水准的制造品质和可靠度。

在日本方面,台积电于2月在熊本为第一座特殊制程技术芯片厂举行了激活典礼,该芯片厂将采用12/16纳米和22/28纳米制程技术,并将如期在2024年第四季进入量产。先前,台积电也与合资伙伴一起宣布计划在日本设立第二座特殊制程技术芯片厂,将采用40纳米、 12/16纳米和6/7纳米等制程技术,以支持消费性、汽车、工业和HPC相关应用的策略性客户。第二座芯片厂计划于2024年下半年开始兴建,并预计于2027年底开始生产。

对于台积电在全球持续产线的布局,魏哲家也表示,针对每个地方产线成本的不相同,已经与客户进行讨论,并获得了客户的同意,将在各地不同产线采用不同价格的措施,以进一步来分摊台积电在各地不同的生产成本。如此,不但可以为客户寻求优化的生产,也可以凸显不同地方生产的价值。

(首图来源:科技新报摄)