根据TrendForce最新研究,AI HPC(高性能计算)对异质集成的需求依赖先进封装完成,其中的关键技术即是TSMC的CoWoS解决方案。然而,随着云计算服务企业(CSP)加速自研ASIC,为集成更多复杂功能的芯片,对封装面积的需求不断扩大,已有CSP开始考量从TSMC的CoWoS方案,转向Intel的EMIB技术。

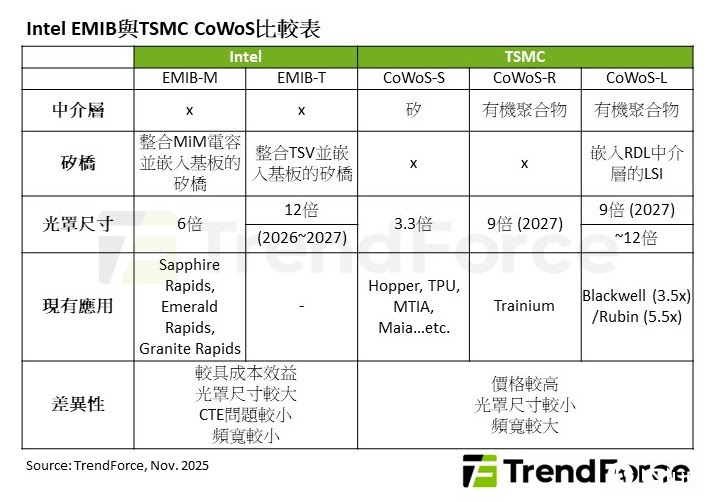

TrendForce表示,CoWoS方案将主运算逻辑芯片、内存、I/O等不同功能的芯片,以中介层(Interposer)方式连接,并固定在基板上,目前已发展出CoWoS-S、CoWoS-R与CoWoS-L等技术。随着NVIDIA Blackwell平台2025年进入规模量产,目前市场需求已高度倾向内置硅中介层的CoWoS-L,NVIDIA下时代的Rubin也将采用,并进一步推升光罩尺寸。

AI HPC需求旺盛导致CoWoS面临产能短缺、光罩尺寸限制,以及价格高昂等问题。TrendForce观察,除了CoWoS多数产能长期由NVIDIA GPU占据、其他客户遭排挤,封装尺寸、以及地缘政治下的美国当地制造需求,也促使Google、Meta等北美CSP开始积极与Intel接洽EMIB解决方案。

TSMC挟技术优势主导先进封装前期市场,Intel以面积、成本优势应战相较于CoWoS,EMIB拥有数项优势:首先是结构简化,EMIB舍弃昂贵且大面积的中介层,直接将芯片使用内置在载板的硅桥(Bridge)方式进行互联,简化整体结构,相对于CoWoS良率更高。其次是热膨胀系数(Coefficient of Thermal Expansion, CTE)问题较小,由于EMIB只在芯片边缘嵌硅桥,整体硅比例低,因此硅与基板的接触区域少,导致热膨胀系数不匹配的问题较小,较不容易产生封装翘曲与可靠度挑战。

EMIB在封装尺寸也较具优势,相较于CoWoS-S仅能达到3.3倍光罩尺寸、CoWoS-L目前发展至3.5倍,预计在2027年达9倍;EMIB-M已可提供6倍光罩尺寸,并预计2026到2027年可支持到8倍至12倍。价格部分,因EMIB舍弃价格高昂的中介层,能为AI客户提供更具成本优势的解决方案。

然而,EMIB技术也受限于硅桥面积与布线密度,可提供的互联带宽相对较低、信号传输距离较长,并有延迟性略高的问题。因此,目前仅ASIC客户较积极在评估洽谈导入。

TrendForce指出,Intel自2021年宣布设立独立的芯片代工服务(Intel Foundry Services, IFS)业务群,耕耘EMIB先进封装技术多年,已应用至自家server CPU平台Sapphire Rapids和Granite Rapids等。随着Google决议在2027年TPUv9导入EMIB试用,Meta也积极评估规划用于其MTIA产品,EMIB技术有望为IFS业务带来重大进展。至于NVIDIA、AMD等对于带宽、传输速度及低延迟需求较高的GPU供应商,仍将以CoWoS为主要封装解决方案。

(首图来源:shutterstock)