AI运算对内存带宽的需求永无止境,也让“定制化HBM”成为半导体厂的兵家必争之地。台积电近日在荷兰阿姆斯特丹举办的2025年OIP(开放创新平台)生态系统论坛中,首度对外披露了关于首代定制化HBM内存的技术蓝图与看法。

根据德国科技媒体Hardwareluxx编辑Andreas Schilling在社交媒体平台上分享的资讯,台积电的观点与美光(Micron)首席商务官Sumit Sadana不谋而合,双方皆认为定制化HBM技术将在HBM4E时代正式落地并普及,台积电更将此类产品定名为“C-HBM4E”。

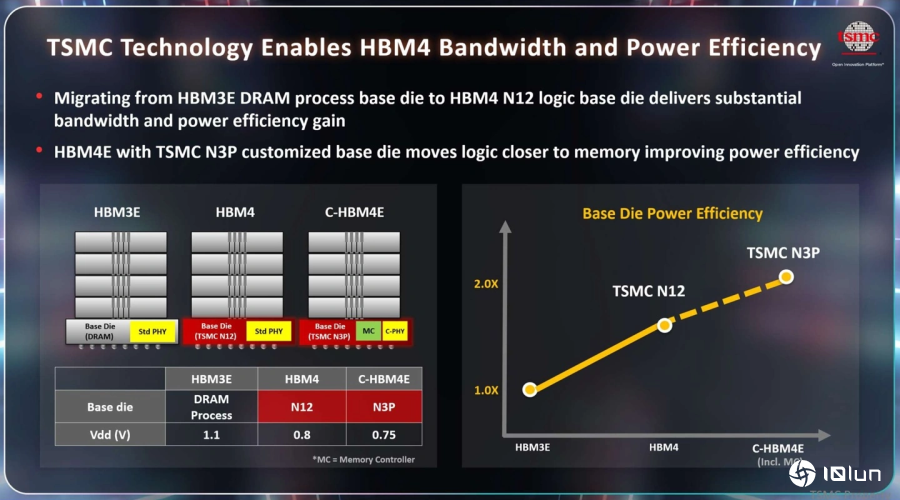

在目前的HBM4时代规划中,台积电为HBM基础裸晶(Base Die)提供了两种不同的制程选项:分别是针对主流市场需求的N12FFC+ 制程,以及专为追求极致性能客户设计的N5制程。

然而,到了更先进的C-HBM4E阶段,为了满足将内存控制器(Memory Controller)直接集成进基础裸晶的需求,同时进一步节省运算芯片的面积,台积电宣布将采用N3P先进制程来打造解决方案。

根据台积电官方说法,采用N3P制程的C-HBM4E基础裸晶,其能源效率将大幅提升,预计可达HBM3E基础裸晶的两倍左右。此外,在功耗控制上也有显著进步,C-HBM4E的Vdd电压将仅有0.75V,比HBM4的电压更低,展现出更优异的省电特性。