晶体管在摩尔定律 (Moore's Law) 的推动下持续提高硅基集成电路 (ICs) 性能,随着尺度微缩至10纳米技术节点以下,已接近操作组件下的物理极限。(数据源:闳康科技;文章编修:科技新报)

本文出自国立清华大学电机系邱博文教授、杨岳强,于闳康科技发布之“二维半导体的新战场:硒氧化铋晶体管”文稿,经科技新报修编。

尽管设计技术协同优化(Design-Technology Co-Optimization, DTCO)与鳍式晶体管(Fin FET)技术将尺度微缩至5纳米技术节点,控制短信道效应仍然是硅基晶体管最严峻的挑战“1”。因此1纳米以下原子级厚度的二维材料晶体管信道已然成为研究热点“2”“3”。

后硅时代的组件候选者二维材料多样化的原子堆砌结构,赋予许多新奇的物理现象与出色的组件性能:超高载流子迁移率“4”“5”、低损耗介电绝缘体“6”、莫尔晶格下的超导体“7”、可调的金半接触“8”、表面掺杂下的弹道传输“9”、异质堆栈下的铁磁序“10”与能谷极化效应“11”等,因而成为后硅时代的组件候选者。在此同时,以硅基为主流的集成电路:FeFET、TFET、DSFET、SFET、FFE等新形态场效晶体管“12”,也正面临极具复杂的集成程序与组件兼容性“13”,必须面对超越冯·诺依曼架构 (Von Neumann Architecture) 所带来新的挑战“14” “15”。

放眼未来,互补式金属氧化物半导体晶体管 (CMOS) 微缩限制的到来,需要更特别的结构设计 (VGAA、VTFET),或取代硅基的新时代材料来满足莫尔定律延续的标准。在此,我们将介绍新颖的二维材料——硒氧化铋半导体,以及它优异的组件特性“16”,有望成为国际组件与系统路线图 (International Roadmap for Devices and Systems, IRDS) 上新的观察员。

发现硅基半导体的研究之路20世纪中期,贝尔实验室的点接触式晶体管研究得到突破,以及接面式晶体管的相应而生,让半导体表面态束缚的电子能够借由场的效应,实现在晶体管内电流放大与整流的作用“17”。然而锗元素先行应用于雷达检波器,使得锗元素晶体管较早作为研究对象。随着时间的推移,科学家发现锗元素在低熔点的限制下,无法在较高的电势场有效操作,同时,科学家也发现同族硅元素具有较高的热稳定性,便转移投注在硅芯片的研究上。

由于“高温气体扩散法”“18”成功在硅芯片上掺杂硼与砷元素,形成P与N型区域半导体;以及利用“热氧化法”“19”来控制二氧化硅薄膜增长,不仅降低硅半导体表面态造成影响,原生氧化层也可作为高界面品质的绝缘体。因此后续大量硅基半导体的研究,也造就了“金属氧化物半导体场效晶体管” (MOSFET) 的问世,为21世纪集成电路带来丰硕的基础。

集成电路技术的演进:手工焊接至22纳米技术集成电路工业的发展,从手工銲锡连接分立组件的年代,演变至硅基集成电路内部集成电阻、电容、晶体管组件。平面化工艺的晶体管可视为积体电子的基础单元。随着对高速运算与存储容量需求的提升,芯片的密度与结构复杂性也持续增加。值得一提的是,在22纳米技术节点以前,尺寸微缩大约0.7倍时,等比降低的能耗与倍数增长的性能,这段时期可谓摩尔定律驱动下的黄金岁月。

然而,当组件尺度进一步缩小至小于20纳米后,闸、源、汲极之间的内部电场开始互相干扰,电子波动特性逐渐主导粒子的行为,此时量子效应所产生的影响不可忽视。小尺寸的非理想效应随之而来,包括阈值电压短信道效应(SCE)、汲极引起的能障降低(DIBL)等。

硅微电子的技术演变:积层型三维集成电路和新颖材料以苹果2022年A16处理器为例,相较1971年代Intel 4044微处理器,晶体管数量约增加了700万倍。由此可知,在晶体管设计的两个重要指标为基准:低漏电流Gate and Source-to-Drain Leakage与开关响应度Subthreshold Swing,设法跳脱出平面结构占地面积不足的窘境。早在1999年由Chenming Hu团队在IEEE发布“Sub 50-nm FinFET: PMOS”鳍式半导体的初型论文后,已预言了从2D MOSFET向3D FinFETs演进的趋势。这一转变不仅使特征尺度能进一步缩小,也有效维持了闸极立体结构对信道的控制能力“20”“21”“22”。2016年由N. Loubet团队以FinFETs为基础下,构建出垂直堆栈的3层“环绕闸极场效晶体管(GAAFETs)”“23”。发展至今,台积电在3纳米节点依然采用技术较成熟的FinFET结构。至于2纳米以下技术节点,未来则必须依赖“积层型三维集成电路3DIC”制程技术的成熟度,在垂直堆栈方向上努力延续莫尔定律。

综观硅微电子学时代的技术演变,尽管鳍式结构(FinFET)代表了当前最先进的晶体管设计,仍然面临着微缩带来的诸多严峻挑战。鳍片的宽度缩小就意味着表面粗糙度与悬键会引起强烈的载流子散射“24”,导致迁移率大幅下降;同时,也伴随着其他非理想效应存在:速度饱和、漏电流与能量耗散的显著增加。另外,也由于块体硅的固有厚度,掺杂的程度往往只能允许单面闸极控制信道表面,极大限制了晶体硅体管的面积使用效率。为了解决上述瓶颈,当前的国际半导体技术路线图 (ITRS) 评估互补金属氧化物半导体技术的下一代要求,迫切需要新颖材料来替代硅在原子尺度上的限制“25”。

欲了解更多二维材料的探索与技术突破,请参阅全文:二维材料的探索与技术突破

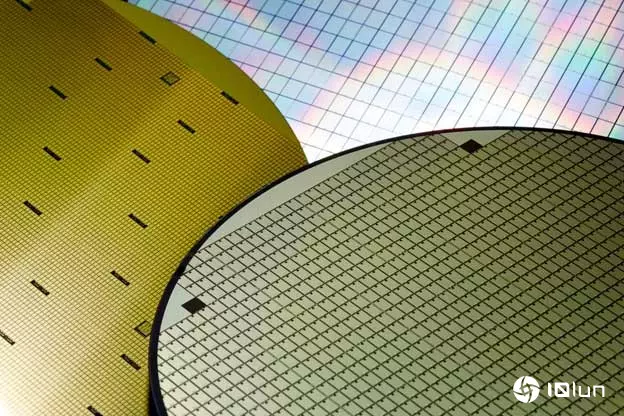

(数据源:闳康科技;首图来源:Shutterstock)

参考文献:“1” Wang, S., Liu, X., & Zhou, P. (2022). The road for 2D semiconductors in the silicon age. Advanced Materials, 34(48), 2106886.

“2” Wang, X., Chen, X., Ma, J., Gou, S., Guo, X., Tong, L., … & Bao, W. (2022). Pass‐Transistor Logic Circuits Based on Wafer‐Scale 2D Semiconductors. Advanced Materials, 2202472.“3” Zhu, K., Wen, C., Aljarb, A. A., Xue, F., Xu, X., Tung, V., … & Lanza, M. (2021). The development of integrated circuits based on two-dimensional materials. Nature Electronics, 4(11), 775-785.“4” Novoselov, K. S., Geim, A. K., Morozov, S. V., Jiang, D. E., Zhang, Y., Dubonos, S. V., … & Firsov, A. A. (2004). Electric field effect in atomically thin carbon films. Science, 306(5696), 666-669.“5” Bandurin, D. A., Tyurnina, A. V., Yu, G. L., Mishchenko, A., Zólyomi, V., Morozov, S. V., … & Cao, Y. (2017). High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nature nanotechnology, 12(3), 223-227.“6” Wang, J. I., Yamoah, M. A., Li, Q., Karamlou, A. H., Dinh, T., Kannan, B., … & Oliver, W. D. (2022). Hexagonal boron nitride as a low-loss dielectric for superconducting quantum circuits and qubits. Nature materials, 21(4), 398-403.“7” Yankowitz, M., Chen, S., Polshyn, H., Zhang, Y., Watanabe, K., Taniguchi, T., … & Dean, C. R. (2019). Tuning superconductivity in twisted bilayer graphene. Science, 363(6431), 1059-1064.“8” Li, W., Gong, X., Yu, Z., Ma, L., Sun, W., Gao, S., … & Wang, X. (2023). Approaching the quantum limit in two-dimensional semiconductor contacts. Nature, 613(7943), 274-279.“9” Jiang, J., Xu, L., Qiu, C., & Peng, L. M. (2023). Ballistic two-dimensional InSe transistors. Nature, 1-6.“10” Wang, X., Xiao, C., Park, H., Zhu, J., Wang, C., Taniguchi, T., … & Xu, X. (2022). Light-induced ferromagnetism in moiré superlattices. Nature, 604(7906), 468-473.“11” Li, J. X., Li, W. Q., Hung, S. H., Chen, P. L., Yang, Y. C., Chang, T. Y., … & Liu, C. H. (2022). Electric control of valley polarization in monolayer WSe2 using a van der Waals magnet. Nature Nanotechnology, 17(7), 721-728.“12” Shen, Y., Dong, Z., Sun, Y., Guo, H., Wu, F., Li, X., … & Ren, T. L. (2022). The trend of 2D transistors toward integrated circuits: Scaling down and new mechanisms. Advanced Materials, 2201916.“13” Akinwande, D., Huyghebaert, C., Wang, C. H., Serna, M. I., Goossens, S., Li, L. J., … & Koppens, F. H. (2019). Graphene and two-dimensional materials for silicon technology. Nature, 573(7775), 507-518.“14” Schram, T., Sutar, S., Radu, I., & Asselberghs, I. (2022). Challenges of Wafer‐Scale Integration of 2D Semiconductors for High‐Performance Transistor Circuits. Advanced Materials, 34(48), 2109796.“15” Liu, C., Chen, H., Wang, S., Liu, Q., Jiang, Y. G., Zhang, D. W., … & Zhou, P. (2020). Two-dimensional materials for next-generation computing technologies. Nature Nanotechnology, 15(7), 545-557.“16” Tan, C., Yu, M., Tang, J., Gao, X., Yin, Y., Zhang, Y., … & Peng, H. (2023). 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature, 1-7.“17” Ayres, R. U., & Ayres, R. U. (2021). The transistor transition: 1945–1969. The History and Future of Technology: Can Technology Save Humanity from Extinction?, 425-466.“18” Chapin, D. M., Fuller, C. S., & Pearson, G. L. (1954). A new silicon p‐n junction photocell for converting solar radiation into electrical power. Journal of applied physics, 25(5), 676-677.“19” Atalla, M. M., Tannenbaum, E., & Scheibner, E. J. (1959). Stabilization of silicon surfaces by thermally grown oxides. Bell System Technical Journal, 38(3), 749-783.“20” Huang, X., Lee, W. C., Kuo, C., Hisamoto, D., Chang, L., Kedzierski, J., … & Hu, C. (1999, December). Sub 50-nm finfet: Pmos. In International Electron Devices Meeting 1999. Technical Digest (Cat. No. 99CH36318) (pp. 67-70). IEEE.“21” Hisamoto, D., Lee, W. C., Kedzierski, J., Takeuchi, H., Asano, K., Kuo, C., … & Hu, C. (2000). FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE transactions on electron devices, 47(12), 2320-2325.“22” Choi, Y. K., Lindert, N., Xuan, P., Tang, S., Ha, D., Anderson, E., … & Hu, C. (2001, December). Sub-20 nm CMOS FinFET technologies. In International Electron Devices Meeting. Technical Digest (Cat. No. 01CH37224) (pp. 19-1). IEEE.“23” Loubet, N., Hook, T., Montanini, P., Yeung, C. W., Kanakasabapathy, S., Guillom, M., … & Khare, M. (2017, June). Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In 2017 Symposium on VLSI Technology (pp. T230-T231). IEEE.“24” Das, S., Sebastian, A., Pop, E., McClellan, C. J., Franklin, A. D., Grasser, T., … & Singh, R. (2021). Transistors based on two-dimensional materials for future integrated circuits. Nature Electronics, 4(11), 786-799.“25” Liu, Y., Duan, X., Shin, H. J., Park, S., Huang, Y., & Duan, X. (2021). Promises and prospects of two-dimensional transistors. Nature, 591(7848), 43-53.