在全球地缘政治与经济不确定性日益加剧之际,创新将是驱动经济繁荣的关键,而人工智能 (AI) 正是核心动力。然而,AI的加速发展导致运算需求快速增长,伴随而来的能源消耗爆炸性增加,这显然成为关键问题。

而尽管算法创新能减少算力需求,且大型语言模型单纯增加算力与数据的效率正在减缓。比利时微电子研究中心 (imec) 总裁兼首席执行官Luc Van den hove预期,AI将加速普及,特别是未来更异质化、代理型与实体型的AI浪潮将会持续推动对庞大运算能力的需求,因此提升运算能效至关重要。

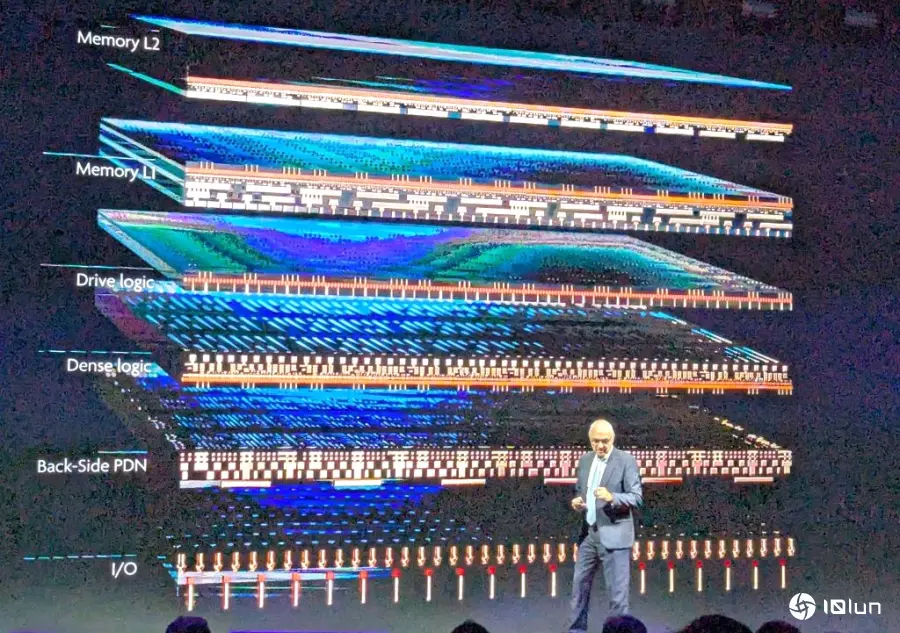

Luc Van den hove在2025 Semicon Taiwan的大师论坛中表示,当前半导体业界正聚焦于运算密度、电源管理和内存瓶颈三大核心挑战,并提出一系列突破性解决方案。首先在运算密度方面,摩尔定律的延续将依赖高数值孔径极紫外光 (High-NA EUV) 微影技术,预计可推动未来二十年的几何微缩。为弥补几何微缩的减速,业界积极利用3D以通过CFET概念垂直堆栈晶体管,以及多层芯片堆栈 (CMOS 2.0),将不同功能芯片层堆栈,每层优化制程,大幅扩展CMOS路线图。最终,通过3D异质集成 (先进封装),构建比单一晶粒更庞大的运算单元,全面提升运算密度。

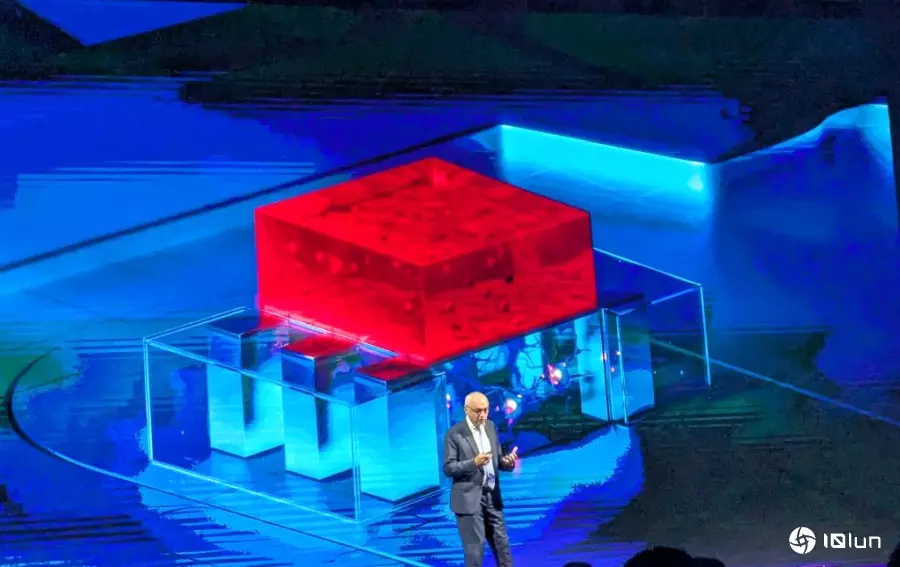

另外,在突破千瓦级功耗极限上,AI芯片的功耗巨大,常超越千瓦,其供电与散热,特别是3D堆栈中的热点管理,是巨大挑战。解决方案包括技术设计优化及直接液体浸入式冷却等高效散热技术。至于,重塑数据流动方面,AI芯片大部分时间与能源耗费在数据移动上。因此,将大量内存集成在逻辑处理区域附近,通过3D堆栈实现,并集成如垂直赛道内存芯片等新型内存。系统层面将优化内存阶层,集成更多运算单元至内存堆栈 (AGM内存)。芯片间的兆位元连接将利用共封装光学互联及主动式硅光子中介层芯片,大幅提升带宽。

Luc Van den hove表示,芯片设计正从传统2D转向全3D优化,结合CMOS 2.0概念,有望诞生软件重构的新架构。这需要算法、芯片架构和技术平台同步突破,并强调硬件软件协同设计。其中,新运算概念也取得突破。Imec已展示超导低温电子学的可扩展性,有望将整个数据中心缩小2,000倍,功耗降低100倍。在量子运算方面,已在量子位元微缩与集成取得进展,开发独特的量子后端架构,为实现大规模量子位元系统奠定基础。

Luc Van den hove强调,当前AI的积极影响已经展现在各领域,如在健康方面,imec利用纳米和微流控技术,在3D芯片上培养人体血脑屏障,精准测试药物,提高脑部疾病治疗效率,为AI药物发现提供模型。而在移动领域,AI推动自动驾驶,imec正通过自动驾驶芯片计划,开发高效、可靠的芯片级集中式运算平台,加速产业创新。

为支持这些突破,imec正进行大规模研发基础设施扩建,投资25亿欧元,将产能翻倍,添加百余台尖端设备,包括ASML的下一代High-NA EUV机台。此扩建获欧盟委员会、CHIPS法案、丹麦政府及工业伙伴支持。面对芯片产业的挑战与机遇,业界必须拥抱颠覆性创新、优先合作并促进开放与透明,共同推动AI时代的创新引擎全速运转。

(首图来源:科技新报摄)